# Ingenious 🤣 Brain

Ingenious e-Brain: A Reliable Partner for Enterprises Dealing with Patent Litigation and Invalidation

## Before delving into the key reasons that make us an apt supporter, let's first understand the need for invalidation or opposition search ...

An invalidation study is used to analyze the closest prior art results before the priority date with respect to the claims of the subject patent, thereby invalidating or revoking an already registered/ granted patent claim or for a pre-grant opposition of a published patent application claim.

By leveraging our invalidation search service, you can check the potency of a granted patent, assess the validity of an established patent, and invalidate the claims of a patent through a prior art search.

## WHY SHOULD YOU CHOOSE US?

- ✓ We believe "Every project has a relevant result"

- ✓ We offer flexible pricing options to cater to client budgets without compromising quality results

- ✓ We provide both novelty and inventiveness-based search strategies to kill an art

- ✓ We follow KSR Seven Rationales for determining the obviousness

- ✓ We deliver high-definition color-coded claim charts to reduce attorney efforts in review

- ✓ We generate a feature matrix for each feature to quickly review the report

- ✓ We have access to paid non-patent databases, such as IEEE, Scopus, Web of Science, etc.

- ✓ We provide the classification data of patents translated into Japanese & Korean languages

- ✓ We categorize results as per the International Search Report (ISR) standard

- ✓ We conduct standard searches on 3GPP & IEEE portal

- ✓ We have proven records of associating with and supporting Fortune 500 companies

### Some Snippets from IeB Research Documents

• High-definition Color coded charts with analyst's comments

| #  | Claims                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Comment on Comparison                                                                              | Comparison<br>Result |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------|

| 1. | Claim 1 A method of manufacturing a<br>printed wiring board having at least one<br>solder bump thereon, the method<br>comprising:                                      | [Summary of the Invention, Column 3, Line 0035 – 0050]<br>In order, to achieve the above objects according to the present invention, a method is provided for evaluating<br>configuration of solder external terminals of a BGA-type tage-based semiconductor device mounted on a mounting<br>board such that the external terminals are joined to lands provided on the mounting board, the method including<br>the steps of:<br>a) obtaining geometric data related to openings of a tape substrate of the semiconductor device, solder balls to be<br>placed at positions corresponding to the openings, and the lands of the mounting board; and<br>b) deriving configuration of the solder external terminal based on the geometric data.<br>With the invention described above, since the estimation is based on known geometric data of the tape openings, solder<br>balls and the lands, the configuration of the solder external terminals can be evaluated accurately and with reduced time.                                                                                                                                                                                                                                                                                                     | In reference to the embodiment<br>Semiconductor device is being used<br>including solder balls     | supported            |

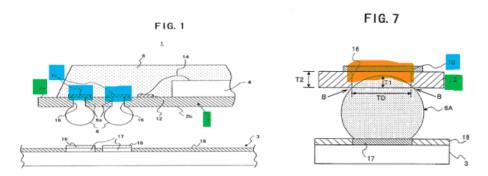

| 7  | forming a solder resist layer on a<br>conductor layer, the solder resist layer<br>having at least one opening that exposes<br>a connection pad of the conductor layer, | [Description of related Art. Column 1, Line 0040 – 0060]<br>FIG. 1 is a Schematic diagram showing a Semiconductor device 1 having a package Structure of a FBGA type. The<br>Semiconductor device 1 generally comprises a tape 2, a Semiconductor chip 4, ball-shape Solder external terminals 6 and<br>a Sealing resin 8.<br>The tape 2 is made of a material Such as polyimide resin. Electrode patterns 10 and bonding pads 12 are provided<br>on a first (upper) Surface 2a of the tape 2. Also, the Semiconductor chip 4 is mounted on the first Surface 2a of the tape<br>2, In order; Dip provide the decircode patterns 10 and the bonding pads 12, a copper layer 2a of the tape 2 and<br>then an etching process is implemented on the copper layer to form predetermined patterns. The electrode patterns<br>10 and the bonding pads 12 are electrically connected by wiring patterns, for thown).<br>Also, wires 14 are provided between the semiconductor chip 4 and the bonding pads 12. Accordingly, the semiconductor<br>chip 4 and the electrode patterns 10 are electrically connected via the wires 14, the bonding pads 12 and the wiring<br>patterns. Further tape opening 16 are formed through the tape 2 at positions corresponding to the electrode<br>patterns 10 of the tape 2. | Tape 2 made of polylmide resin which is<br>considered as solder resist layer on<br>electrode plate | Supported            |

## • Key feature matrix with clear indications regarding partially and inferentially disclosed features

| LEG  | GAL STATUS                                                                                                                                                                                        | Granted      | Pending | Lapsed | Expired                                                      |       |             |                    |             |              |              |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------|--------|--------------------------------------------------------------|-------|-------------|--------------------|-------------|--------------|--------------|--|

| #    |                                                                                                                                                                                                   | Kou footu    |         |        | Colour represents inferentially (I) /partially (P) supported |       |             |                    |             |              |              |  |

| "    |                                                                                                                                                                                                   | Key features |         |        | WO201814666                                                  | A2 KR | 101065797B1 | <u>US7637040B2</u> | FR2897517A1 | CN113106720B | CN103422334A |  |

| 1    | An ironing device comprising:                                                                                                                                                                     |              |         |        | ~                                                            |       | ~           | *                  | *           | *            | ~            |  |

| 1(a) | a glove configured to be worn on a user's<br>hand and including at least one contact<br>portion configured to be placed in<br>contact with a garment,                                             |              |         |        | ~                                                            |       | *           | *                  | *           | *            | ~            |  |

| 1(b) | ironing means that are integral with said<br>glove and arranged at least along said<br>contact portion                                                                                            |              |         |        | V                                                            |       | *           | T                  | *           | р            | ~            |  |

| 1(c) | <ul> <li>control means operatively connected to</li> <li>said ironing means and configured to</li> <li>control the operation of said ironing</li> <li>means, and characterised in that</li> </ul> |              |         | to     | ✓                                                            |       | *           | *                  | ×           | I            | ×            |  |

| Symbols | Definition                                                                                                                                                            |  |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| ~       | Fully supported: - The patent reference supports all the elements of the subject patent claims                                                                        |  |  |  |  |  |  |

| I       | Inferentially supported: - The patent reference has disclosed a broad concept and does not explicitly disclose the certain concept as disclosed in the subject patent |  |  |  |  |  |  |

| Р       | Partially supported: - The patent reference has disclosed certain elements of the subject patent claim and has not revealed some other parts of that claim            |  |  |  |  |  |  |

| ×       | Not supported: Key Feature not found                                                                                                                                  |  |  |  |  |  |  |

#### • Category-wise segregation of findings

#### **1.1 LIST OF PATENT RESULTS**

1.1.1 Tier-I (Category X)

| #     | Publication Number   | Title                                                                                                                                    | Associated Patent<br>Law | Publication Date      | Filing Date           | Priority Date         | Assignee(s)    | Inventor                |

|-------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|-----------------------|-----------------------|----------------|-------------------------|

| 1     | JPXXXXXXXX9A         | POWER TOOL                                                                                                                               | 35 U.S.C. 102 (b)        | September 18,<br>2008 | March 1, 2007         | March 1, 2007         | PANASONIC      | Sunao Arimura et al.    |

| 2     | JPXXXXXXXXXX8A       | POWER TOOL                                                                                                                               | 35 U.S.C. 102 (a)        | April 7, 2011         | September 25,<br>2009 | September 25,<br>2009 | PANASONIC      | Hiroshi Miyazaki et al. |

| 3     | JPXXXXXXXX7A         | COMMUNICATION SYSTEM AND<br>METHOD FOR IMPLEMENTING<br>COMMUNICATION THROUGH<br>ELECTRIC SUPPLY TERMINAL IN<br>DIRECT CURRENT POWER TOOL | 35 U.S.C. 102 (b)        | August 11, 2005       | January 31, 2005      | January 30, 2004      | BLACK & DECKER | Daniele C Brotto et al. |

| 1.1.2 | Tier-II (Category Y) |                                                                                                                                          |                          |                       |                       |                       |                |                         |

| #     | Publication Number   | Title                                                                                                                                    | Associated Patent<br>Law | Publication Date      | Filing Date           | Priority Date         | Assignee(s)    | Inventor                |

| 1     | JPXXXXXXXXQA         | BATTERY PACK AND ADAPTER                                                                                                                 | 35 U.S.C. 102 (b)        | August 1, 2007        | March 1, 2001         | March 1, 2001         | MAKITA         | Hirokatsu Yamamoto      |

Are you afraid of dealing with potential infringement lawsuits or claims of patent violation, want to assess the validity or strength of existing patents, or challenge the existing allegations made by other patent holders, aiming to either invalidate or narrow down the scope of their patents?

Worry not! ... Our seasoned IP experts manage your patent portfolio and help you precisely craft and choose patents, trademarks, and copyrights with minimum risk of being litigated.

Reach out to us today to know how we can help you with patent safeguarding, monetization, litigation, and infringement-related lawsuits by emailing at <u>contact@iebrain.com</u>.

**Future-Proofing Businesses**

Visit Us: www.iebrain.com

Contact Us: contact@iebrain.com

#### INDIA (HQ)

Unit 207-208, 2<sup>nd</sup> Floor, Welldone Tech Park Sohna Road, Sector 48, Gurugram, Haryana 122018

Phone No. - +91 124 429 4218

#### USA

646 Sutton Way #1006 Grass Valley, United States CA 95945

Phone No. - +1 347 480 2054

#### UK

13 Freeland Park, Poole, Dorset, United Kingdom, BH16 6FH

Phone - + 44 207 193 3548